cocotb: A Beginner’s Guide to Python-Based Hardware Verification

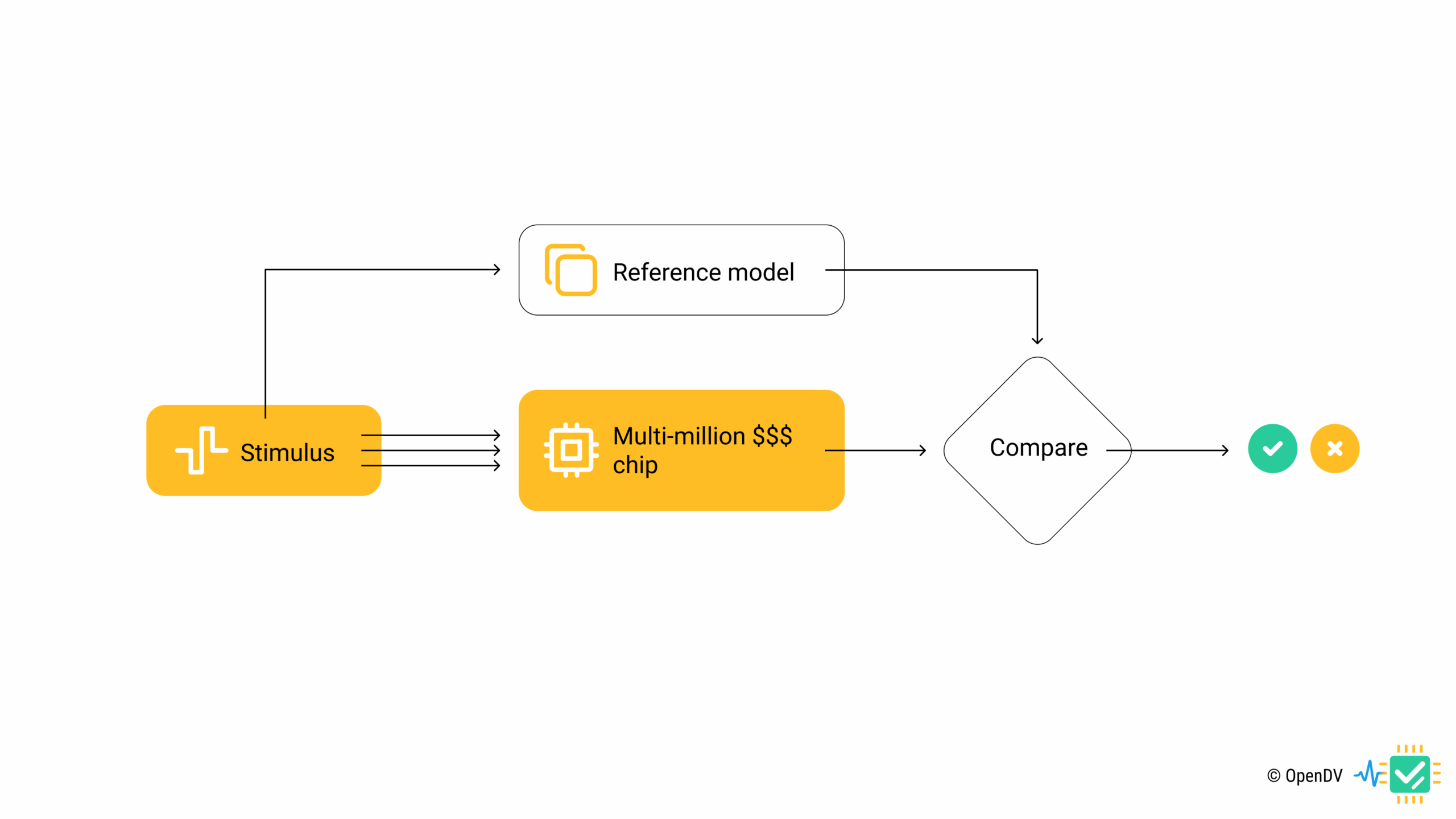

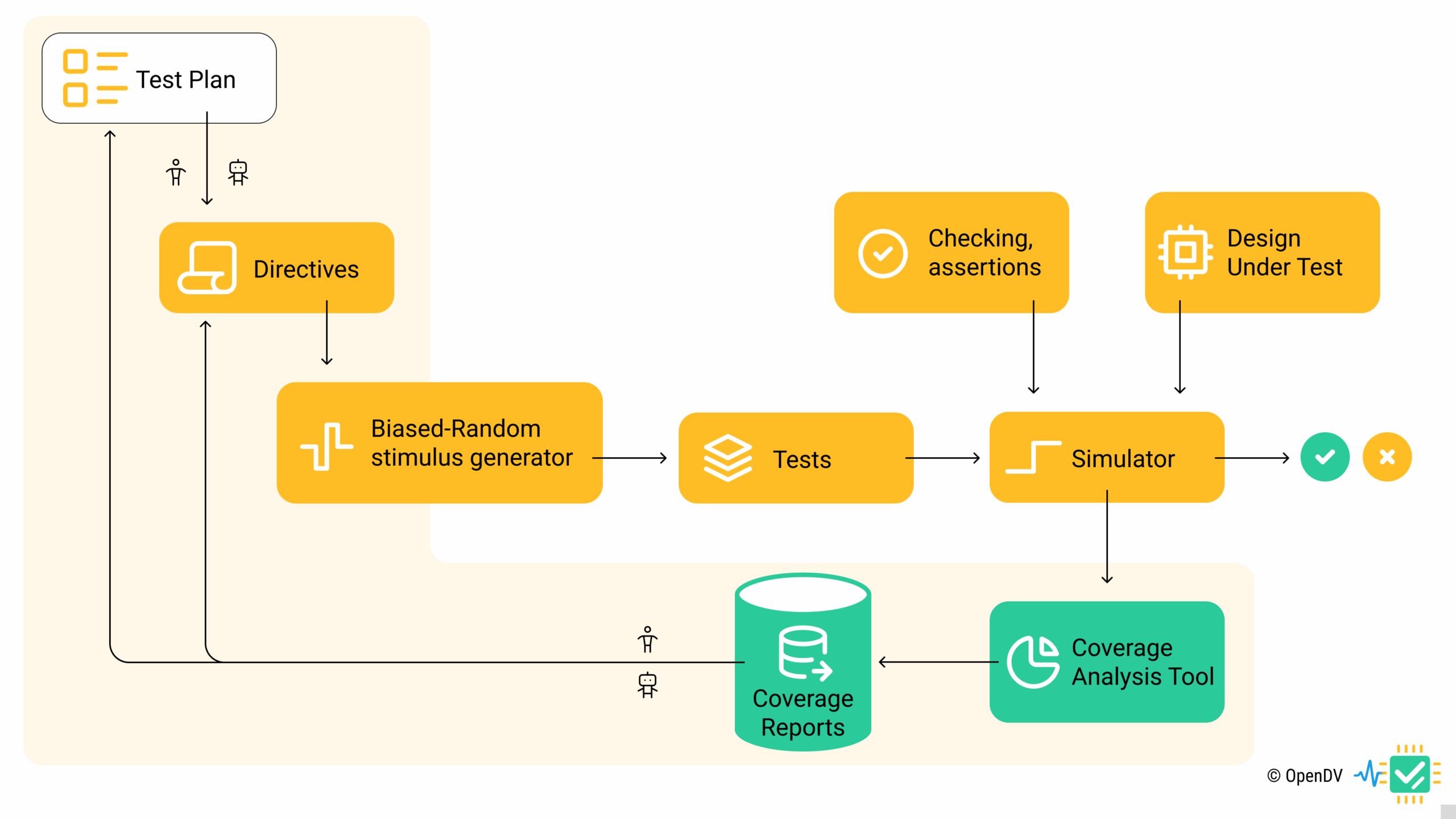

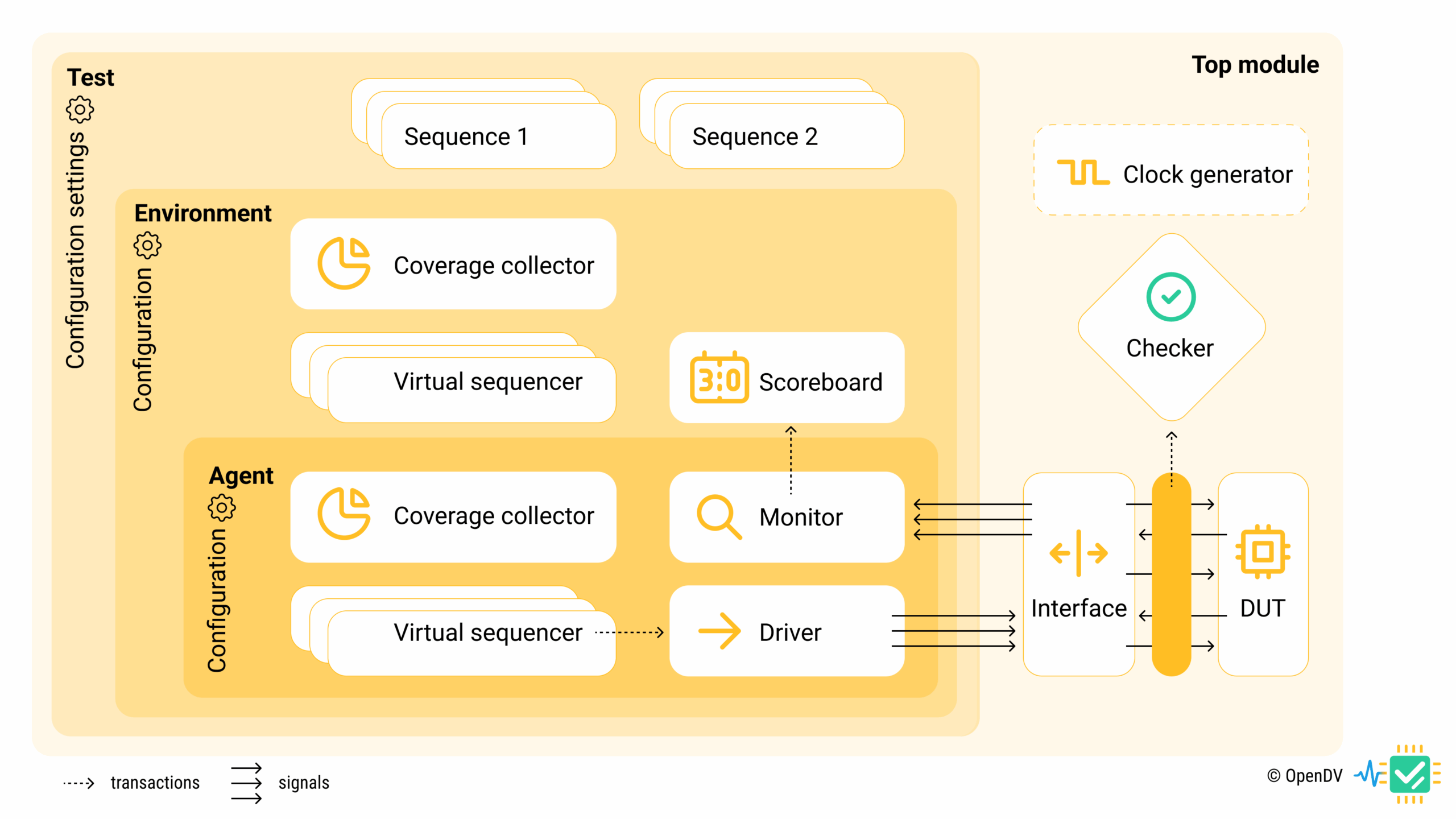

Hardware verification has traditionally been dominated by SystemVerilog and other specialized hardware description languages. However, cocotb (Coroutine-based Cosimulation TestBench) is changing the game by bringing the power and simplicity of Python to hardware verification. This tutorial will introduce you to cocotb, show you how to set it up, and walk through practical examples that demonstrate […]