Learn hardware design verification

OpenDV is your comprehensive educational platform for learning hardware design verification. Whether you are a student taking your first verification course or an engineer transitioning into verification roles, we provide the structured learning path you need to succeed.

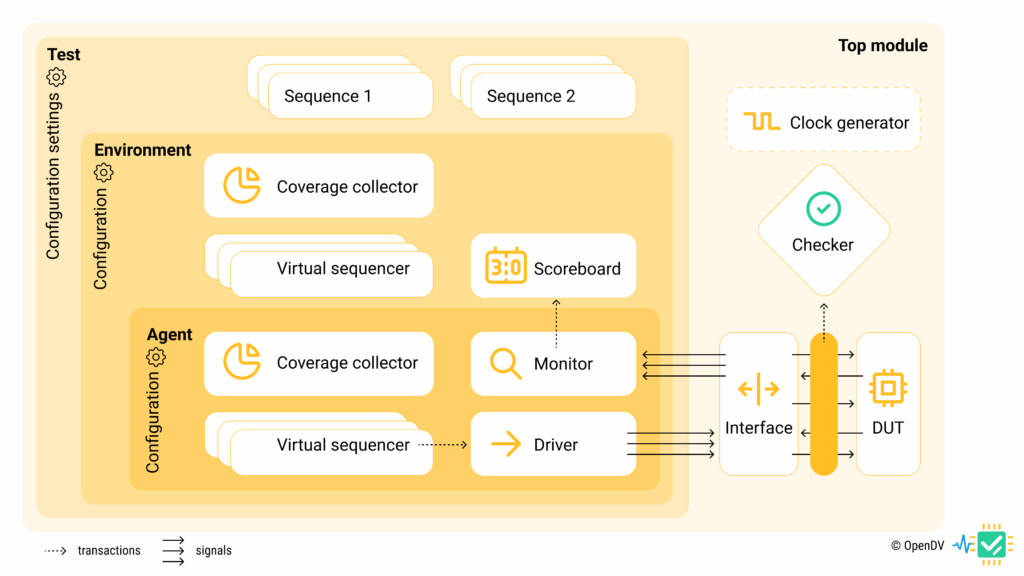

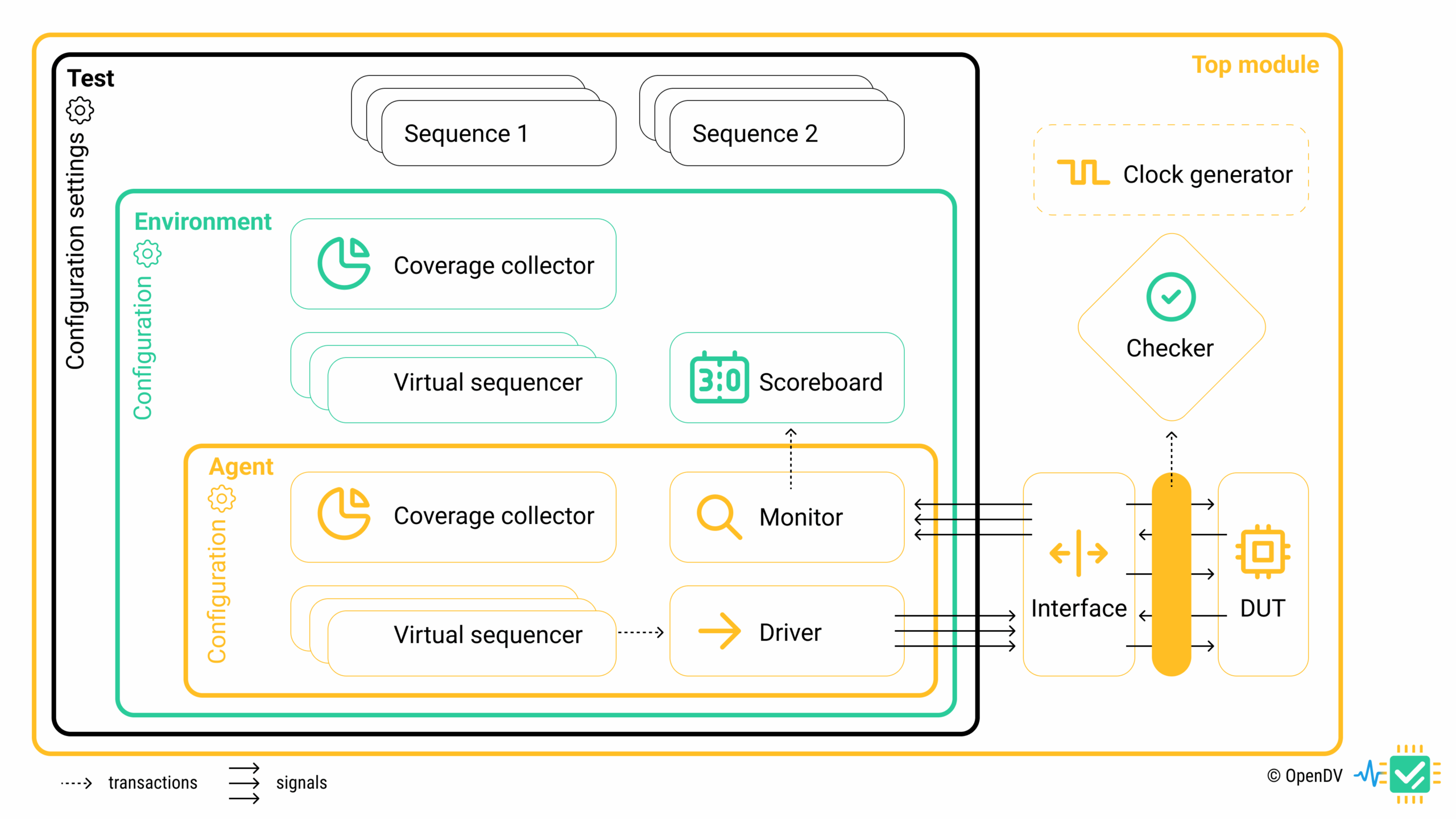

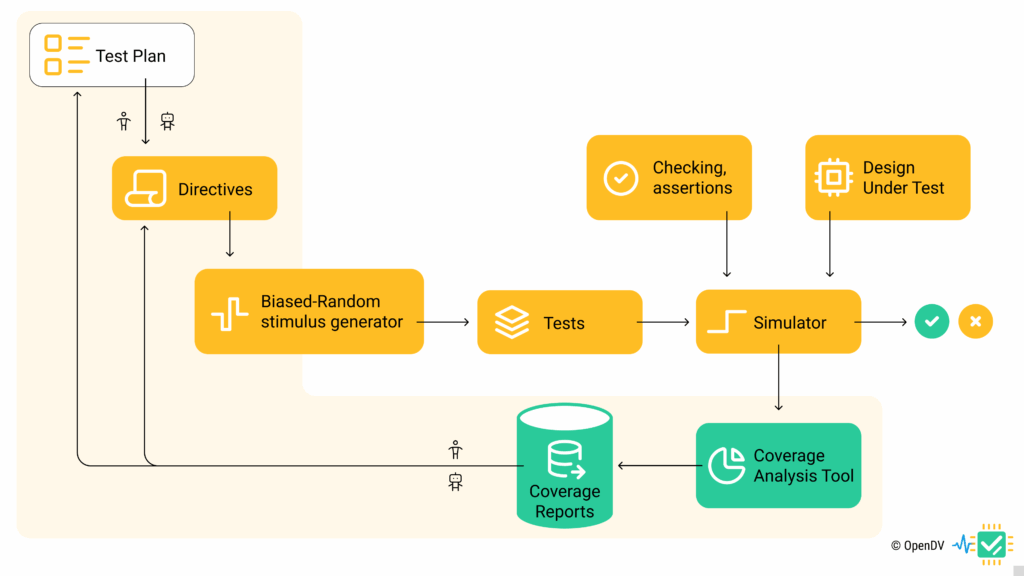

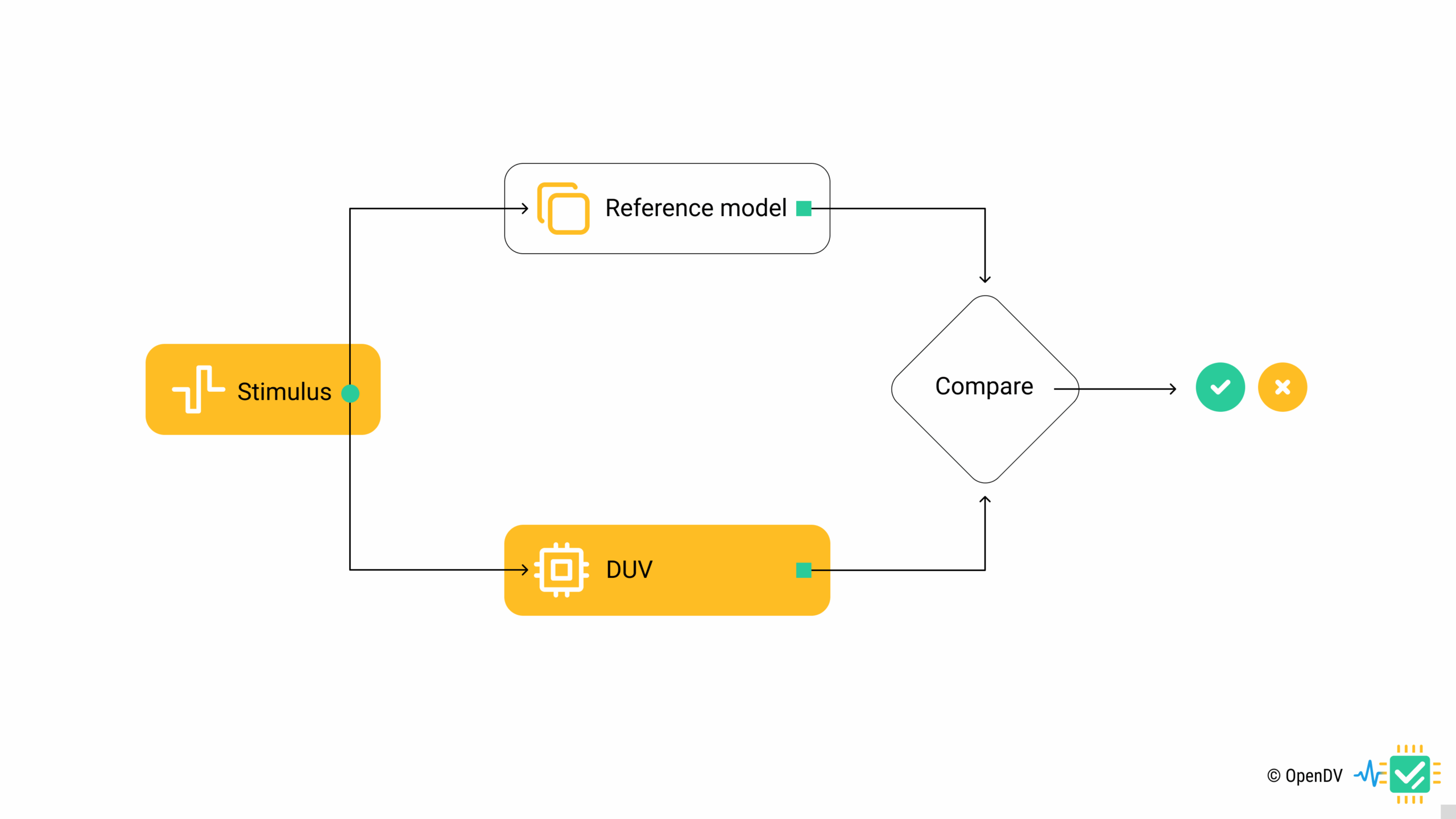

Testbench architecture

Understand how to structure verification environments, including stimulus generation, design under test (DUT) interfaces, response checking, and the overall testbench hierarchy.

Assertions

Develop proficiency in SystemVerilog for verification (classes, randomization, interfaces) and assertion-based verification (SVA). This includes understanding temporal logic and writing assertions.

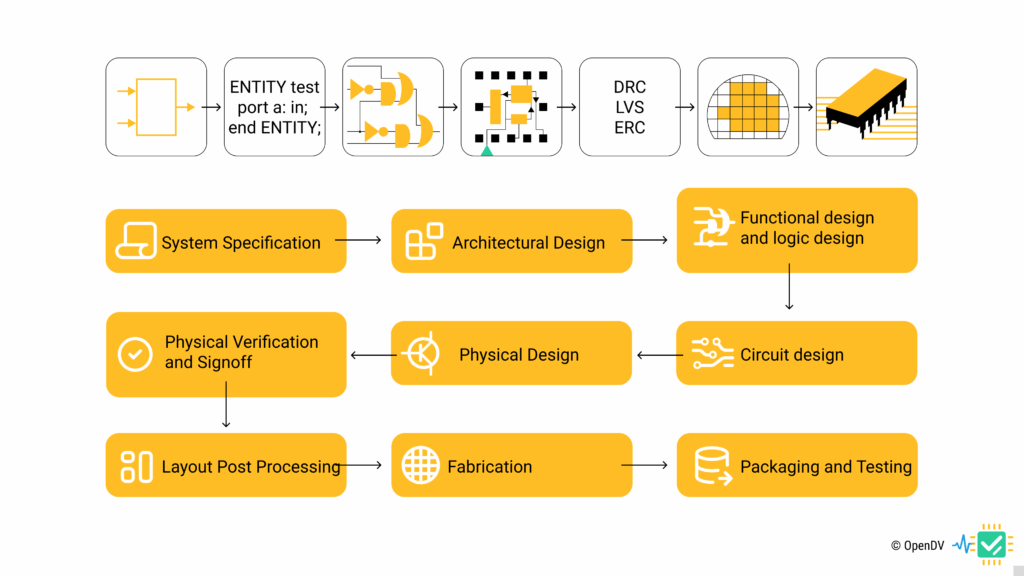

Coverage

Understand functional coverage, code coverage, and assertion coverage for thorough verification. This includes defining coverage goals, understanding coverage closure, and using coverage data to guide verification efforts.

LLM Applications

Explore how Large Language Models are transforming hardware verification through AI-powered test generation, automated testbench creation, and intelligent debug assistance. Learn to leverage LLMs for generating SystemVerilog code, creating verification plans, analyzing coverage gaps, and accelerating common verification tasks.

Why does verification matter?

Modern semiconductor designs contain billions of transistors and complex functionality that must work flawlessly in mission-critical applications. A single bug can cost millions in recalls, delays, and lost reputation. Verification engineers are the guardians of chip quality, ensuring designs work correctly before they reach silicon.

What will you learn?

You will learn the three pillars of simulation-based verification: Stimulus, Checking, and Coverage. This includes generating comprehensive stimulus that exercises your design under all conditions, implementing robust checking mechanisms to detect when your design behaves incorrectly, and developing coverage metrics to measure verification completeness and guide your testing efforts.